1.はじめに

巷には安価で簡易的に使えるクロック生成デバイスとしてSilicon Laboratoriesのsi5153aが有名である。今回とある装置のクロック源して使用できるかどうかこの素性を調べてみることにした。

使用したい諸元(要求仕様)は以下の通り。

- 周波数:10~100MHz

- 出力レベル:0~10dBm

- 2ch間の位相調整ができること

- ジッタがなるべく小さいこと=位相ノイズが小さいこと

- マイコン制御できるもの

この条件で探すとSililabのsi5351aとAnalogdevicesのDDSのAD9959があり、以下はその比較

両者は最終アプリケーションでの目的が若干異なるため、信号生成の方法が異なる。

AD9959のほうが高価ではあるが、性能もよい。

2.SGに使用するデバイス選定

| 項目 | Si5351A(Silicon Labs) | AD9959(Analog Devices) |

|---|---|---|

| デバイス種別 / 方式 | クロックジェネレータ(PLL + 分数分周 MultiSynth) | DDS(Direct Digital Synthesizer)(4ch DDS + DAC) |

| 主用途 | デジタルIC向けクロック生成(任意周波数クロック、逓倍/分周、複数クロック) | 多ch同期の正弦波/IF信号生成、位相/振幅/周波数制御、変調/掃引 |

| 出力チャンネル数 | 最大8出力(品種/パッケージで3/4/8出力品が存在) | 4出力(同期DDSチャンネル) |

| 出力信号 | CMOS/LVCMOSクロック出力(デジタル) | アナログDAC出力(電流出力、外付けLPF等で正弦波化)/10-bit DAC内蔵 |

| 出力周波数レンジ | 2.5 kHz ~ 200 MHz(Output Clock Characteristics) | 参照クロック最大 500 MSPS(REFCLK条件次第) ※実用出力帯域は用途・フィルタ設計・ナイキスト等に依存 |

| 周波数分解能 | “任意周波数生成”が主眼(デジタルクロック生成) | 周波数チューニング分解能 ≤0.12 Hz |

| 位相制御 | 出力位相オフセット機能あり | 14-bit 位相オフセット分解能 |

| 振幅制御 | 基本はクロック振幅=電源/ドライブ設定 | 10-bit 振幅スケーリング分解能 |

| 変調・掃引 | スプレッドスペクトラム等(EMI低減) | リニア掃引、最大16レベルの周波数/位相/振幅変調(ピン選択) |

| 参照入力 / 基準 | クリスタル 25–27 MHz、CLKIN 10–100 MHz | REFCLK:PLL逓倍器あり(4~20倍)、水晶発振器サポート(20~30 MHz) |

| 電源 | コア電源 2.5 V or 3.3 V(推奨条件) | DDSコア 1.8 V、I/O(SPI) 3.3 V |

| インターフェース | I²C(7-bit、100 kbps/400 kbps、バースト転送) | SPI(シリアルI/O) |

| ジッタ等の観点 | 代表的に **周期ジッタ(pk-pk)**等が規定(構成依存) | DAC/DDS由来のSFDR/スプリアス設計が焦点(用途依存)※製品として10-bit DAC等を規定 |

| 動作温度 | –40~+85°C(推奨条件) | –40~+85°C |

| パッケージ | 10-MSOP / 16-QFN / 20-QFN など(ファミリ) | 56-lead LFCSP |

3. si5351aデバイス

3.1 概要

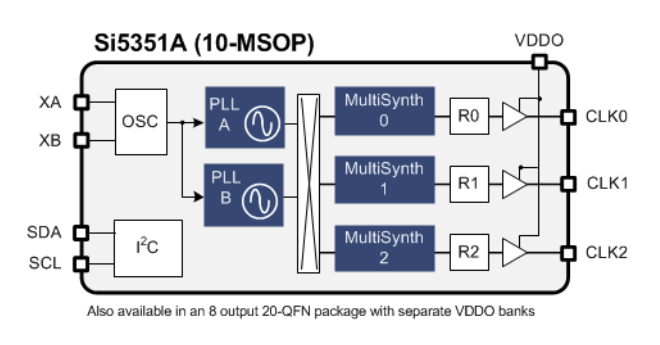

I2C経由で周波数設定や位相制御を行うことができる。ただしその組み合わせは多く、「周波数精度」「ジッタ」「周波数帯域」の何を優先させるかにより内部PLLの分周期の設定方法が変わってくる。ここでは「周波数100MHz」「低ジッタ」を優先に調整していくことにする。

内部ブロックとしては左にあるように2つのPLLをもち3系統の出力となっている。

PLLAでCLK0,CLK1を動作させることにより同期した波形ができるので、同じ分周比にして、delayパラメータを設定することで2つの出力間の位相を調整することが可能である。ただし、周波数によって位相調整範囲の制約がありそうです。

3.2 位相制御特性

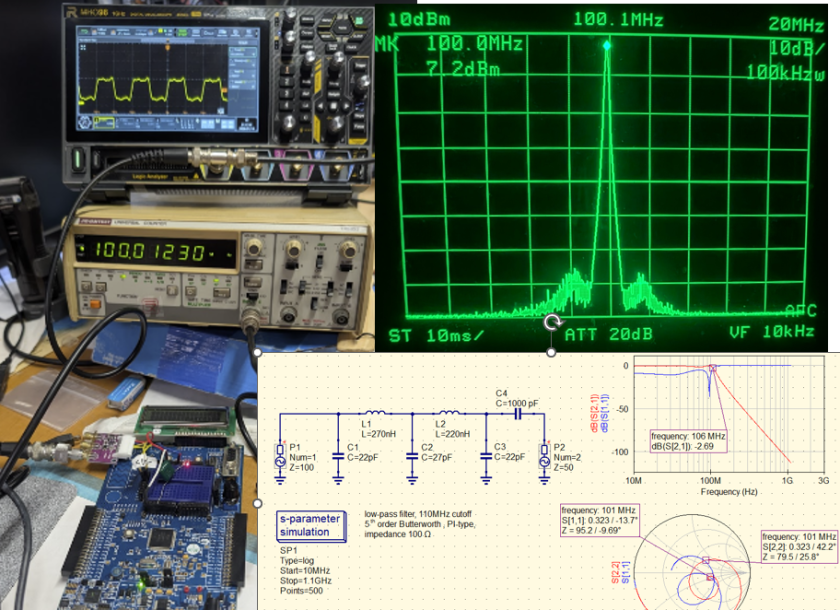

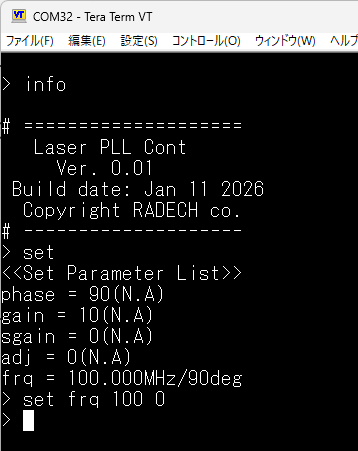

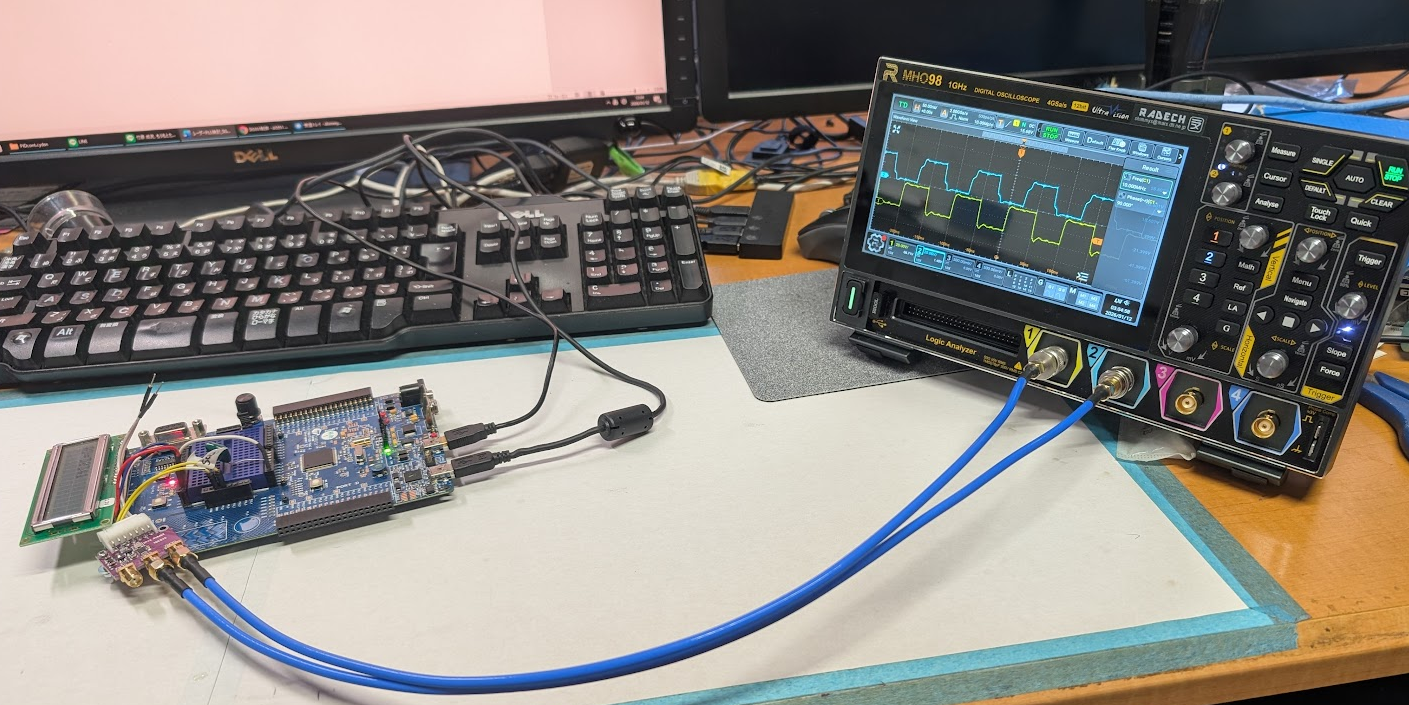

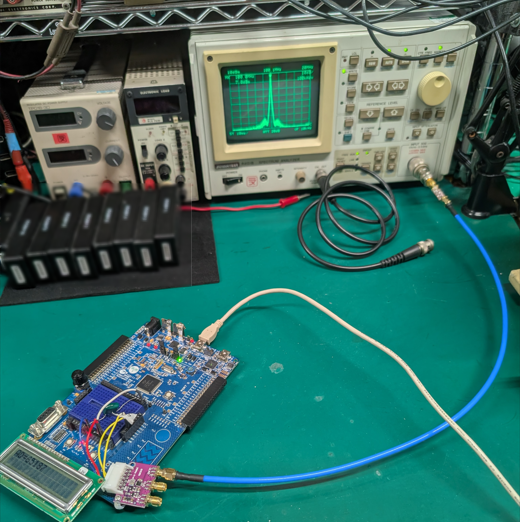

☜ここで詳細説明は省略するが、PSoCマイコンで制御プラットフォームソフトを構築し、その上で、si5351aデバイスを設定するライブラリ(ドライバー)を作成し、ターミナルから制御できるツールを作成した。

評価用の制御SWをPSoCで作成。コンソール風なUIでまとめる

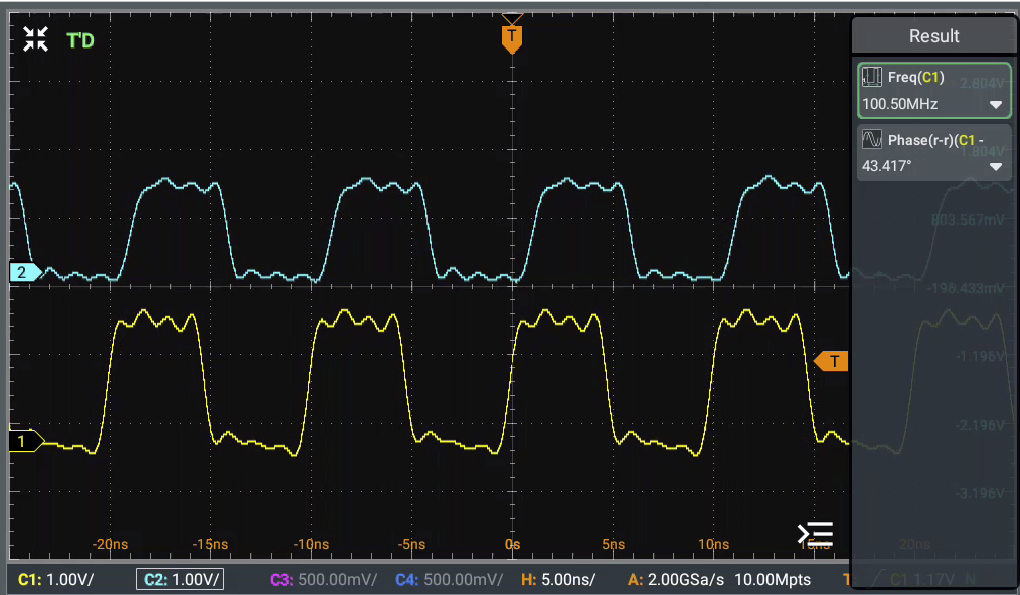

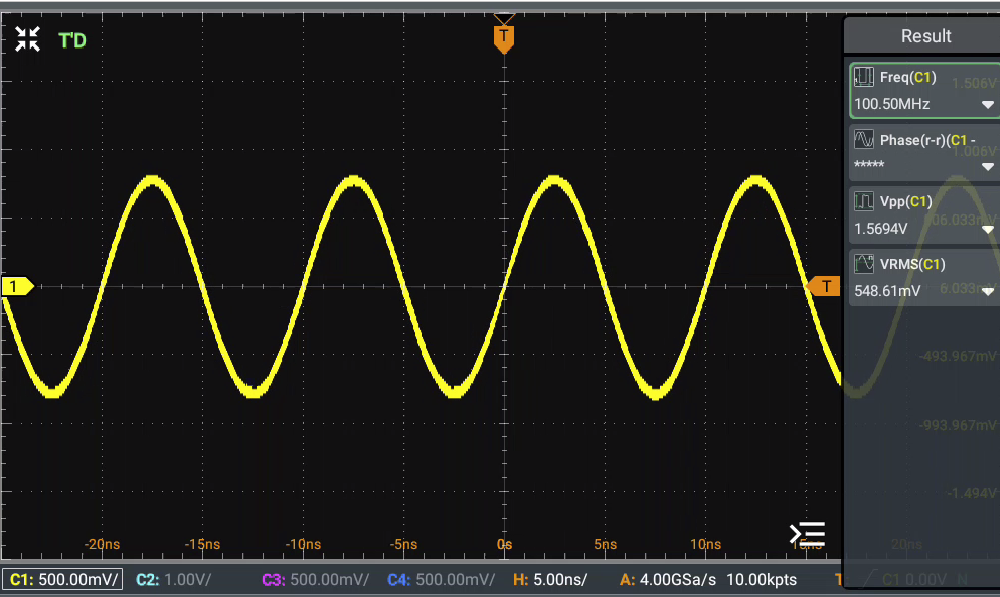

※オシロの入力は50Ω受けに設定。our0,out1間の位相を測定

おおよそ狙い通りの位相回転制御ができた。out2の出力振幅は若干低いようだ。ばらつき?

si5351aデバイスで100MHzを出力する場合、内部分周比とdelayレジスタの関係で位相制御分解能が最小45度になってしまう。出力周波数を仮に10MHzにすると、位相制御分解能は数度で制御することが可能である。

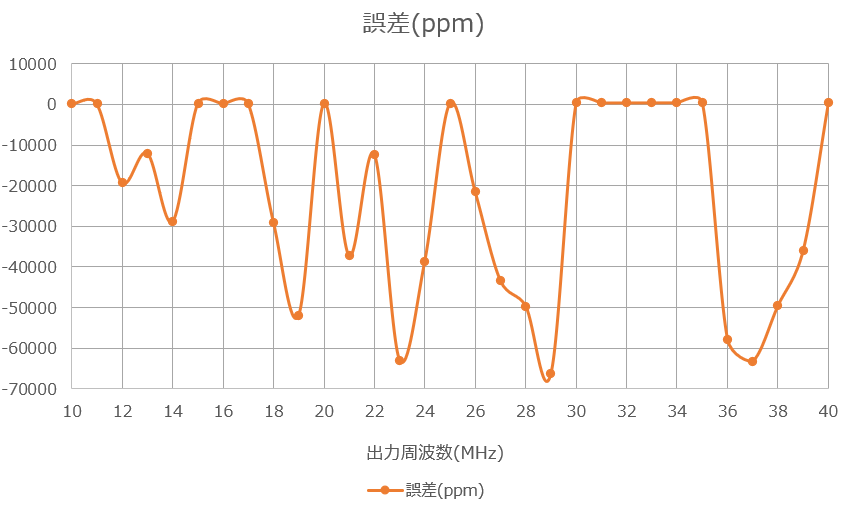

3.3 周波数設定精度

3.4 10MHzの場合

オシロ受けは1MΩ

周波数を10MHzに設定すると位相設定分解能は5度刻みでもいけそうだ。

また出力電圧もout1,2でほぼ同じレベルになってくる。

4. Low Pass Filter

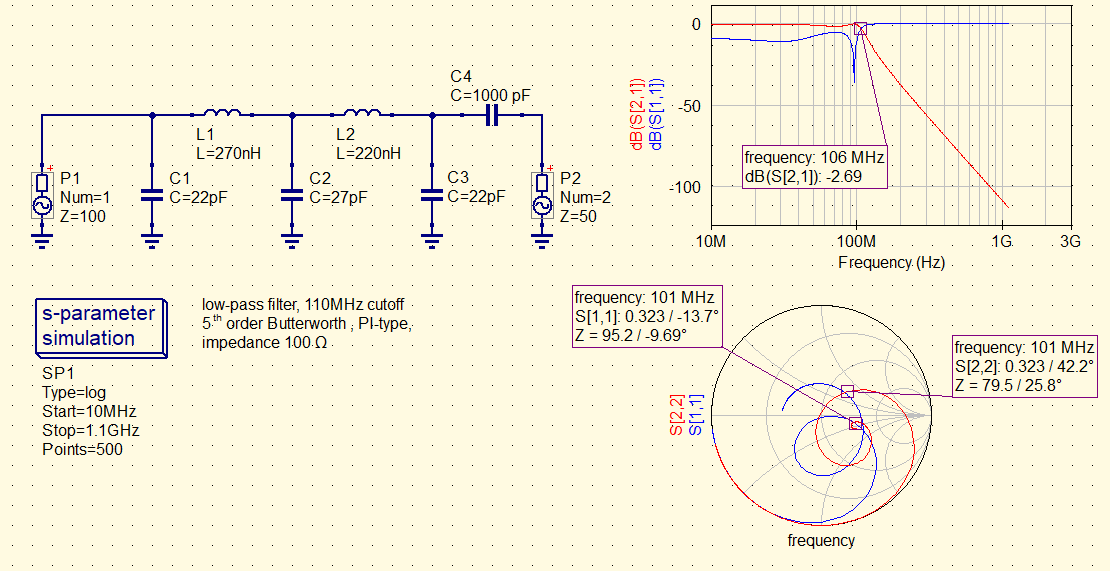

si5351aは方形波出力のクロック発振源なのでSIN波が欲しいときは、si5351aで生成された方形波出力を100MHzのLOW PASS Filterで正弦波にすることになる。

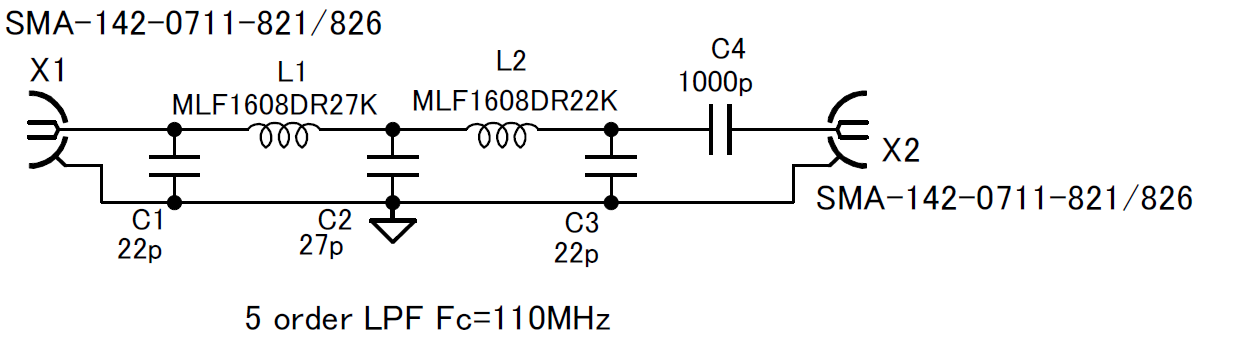

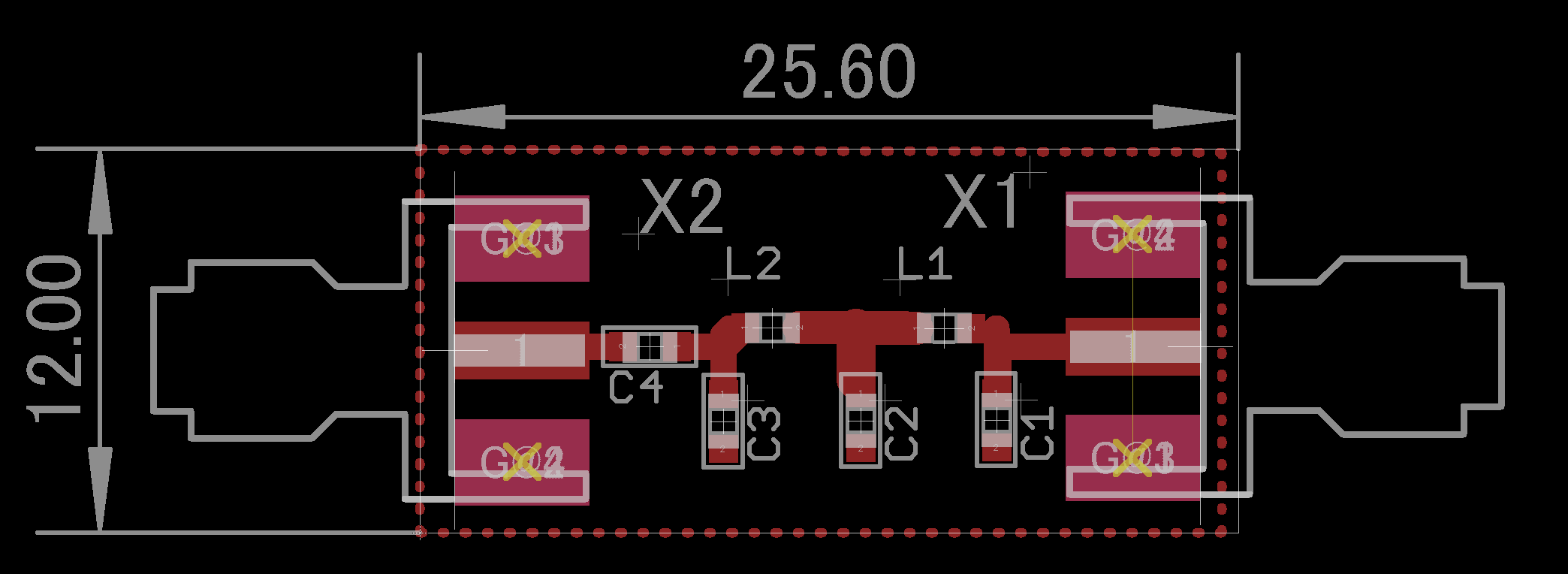

ここでの注意はsi5351aの出力インピーダンスは約100Ωで、本装置先に接続するデバイスの入力インピーダンスはおそらく50Ωになっているという前提で以下のような5次、LCバタワースフィルタを設計・シミュレーションおこなった。

5次なので理想的には100dB/decadeのroll offとなる。シミュレーション上もそれに近くなっているが実際に使用するC,Lは自己共振や損失があるため、理想通りの特性にはならない。

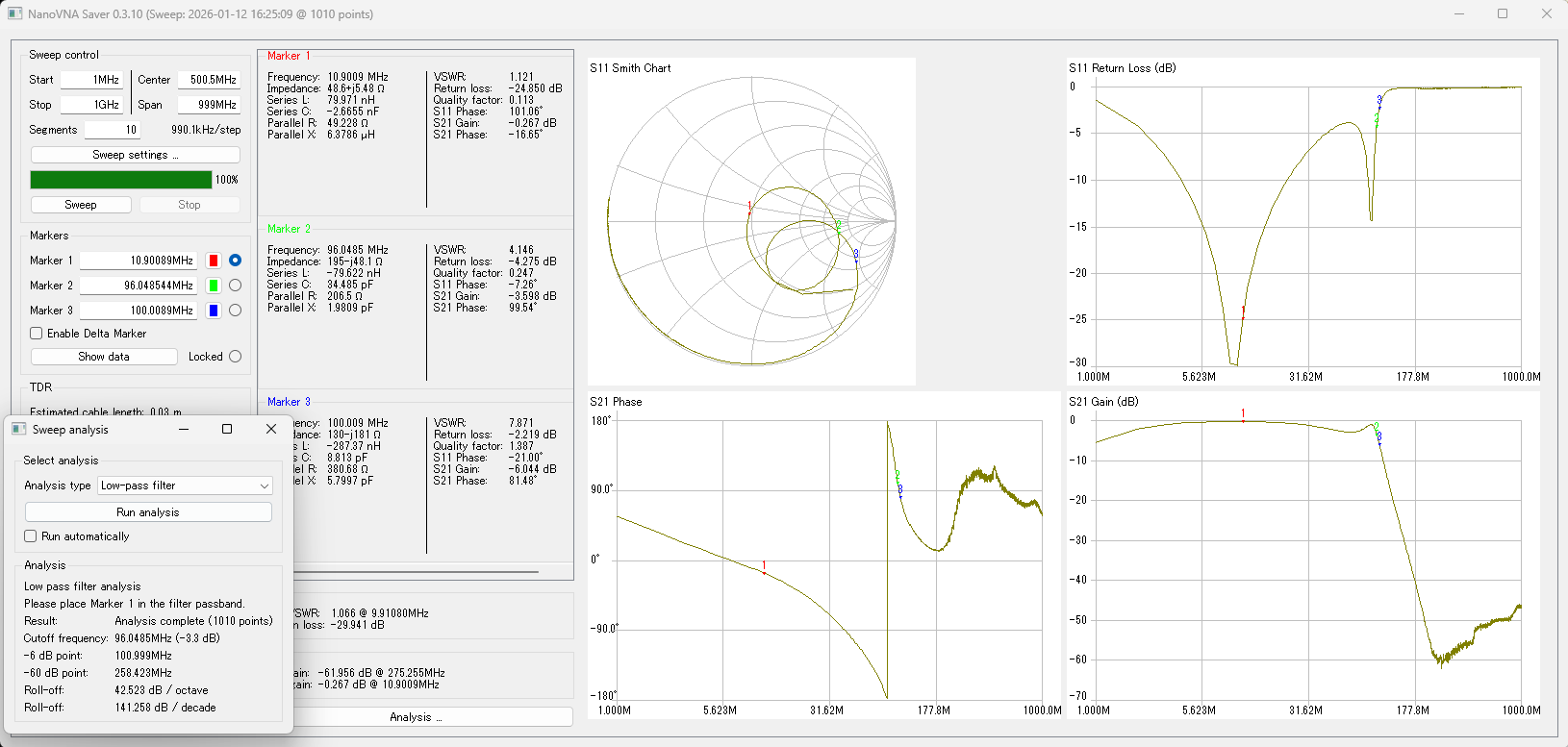

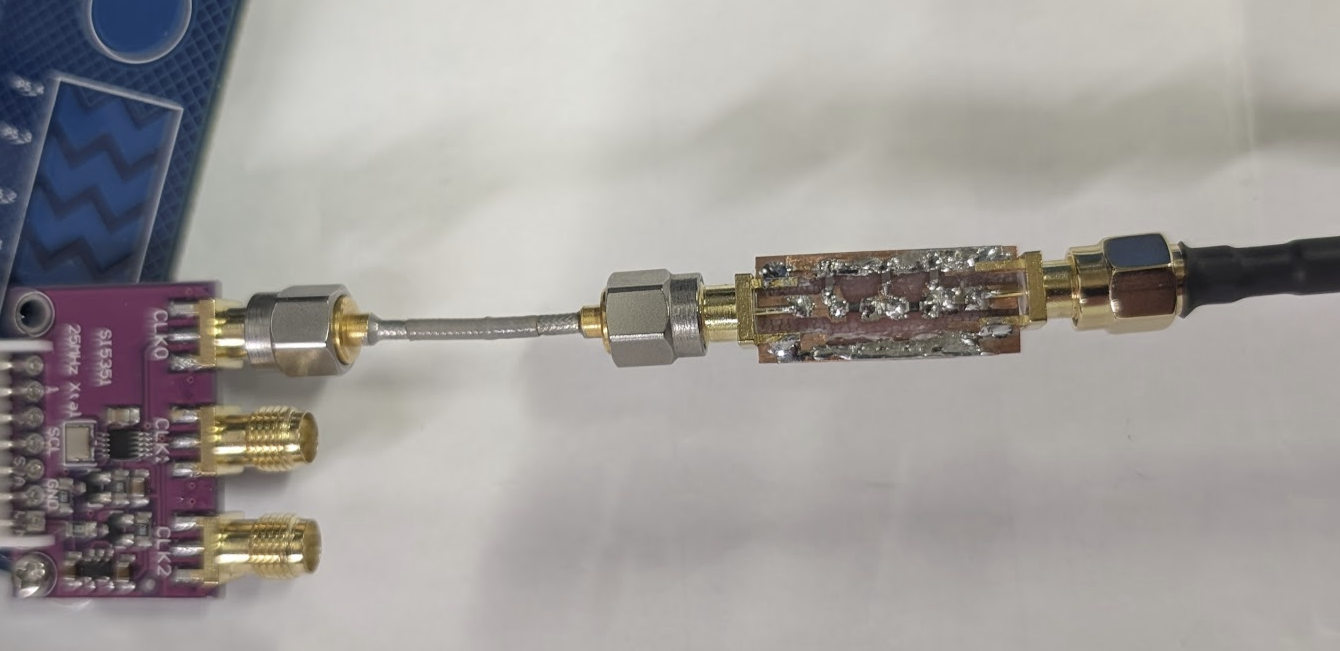

ほぼシミュレーション通りの特性となった。

4. 信号品質の確認

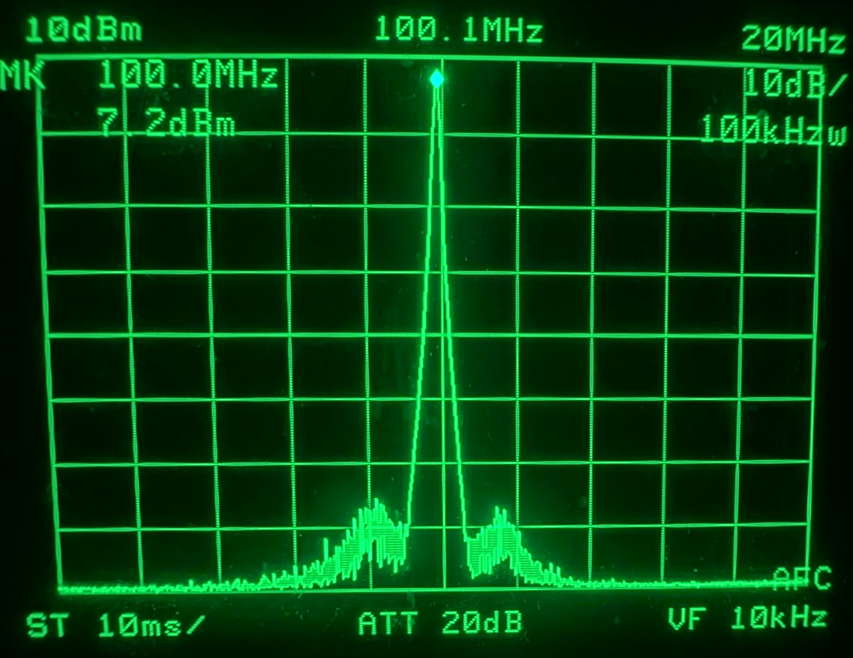

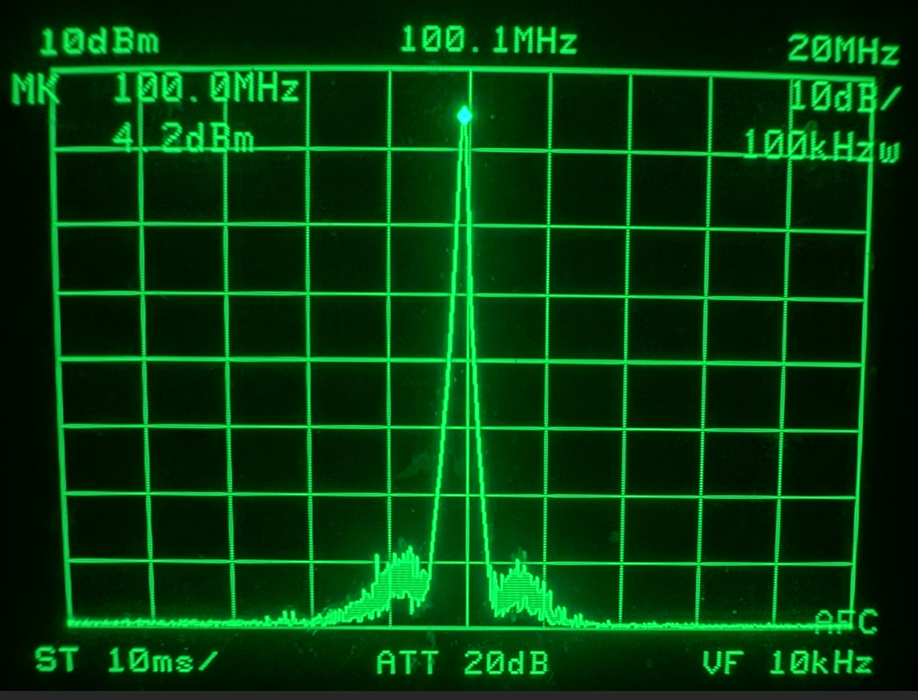

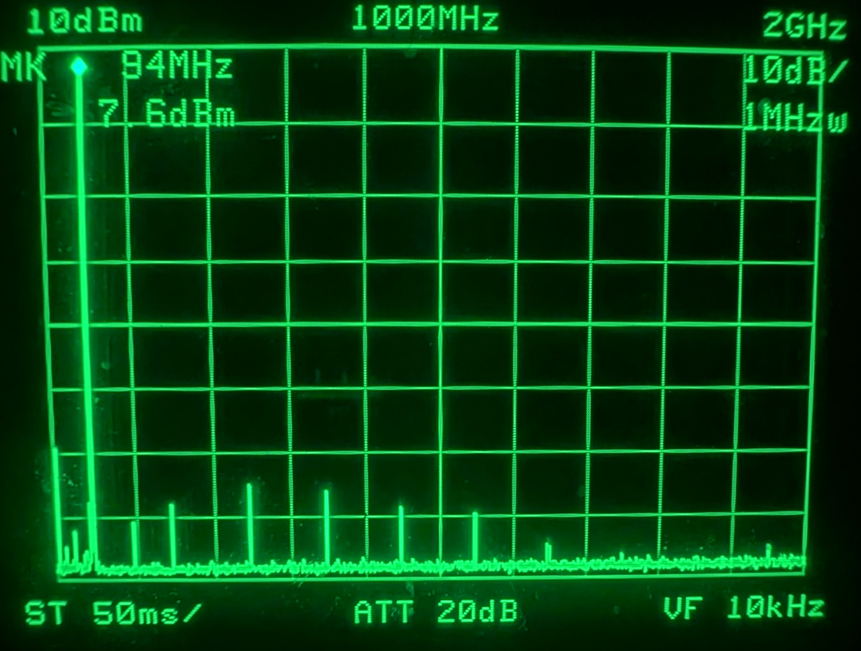

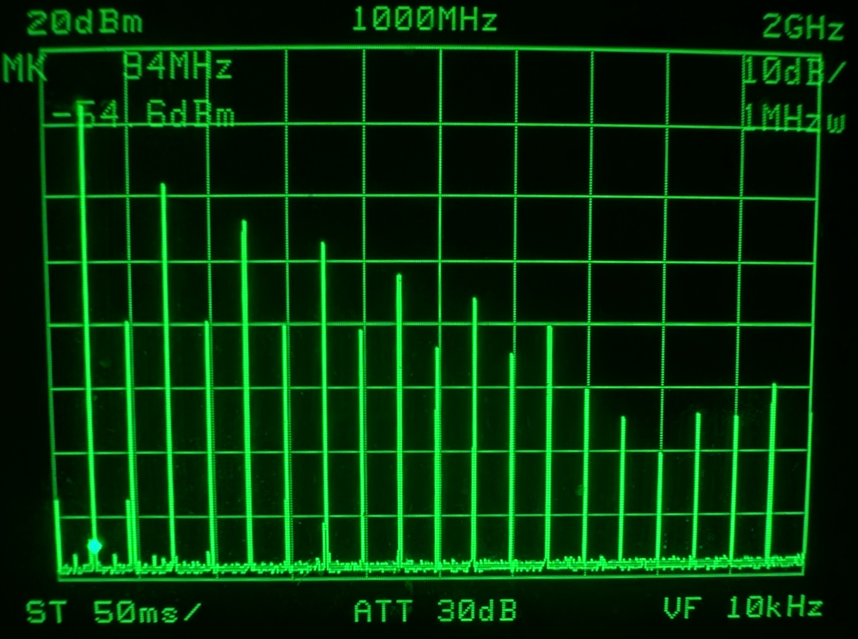

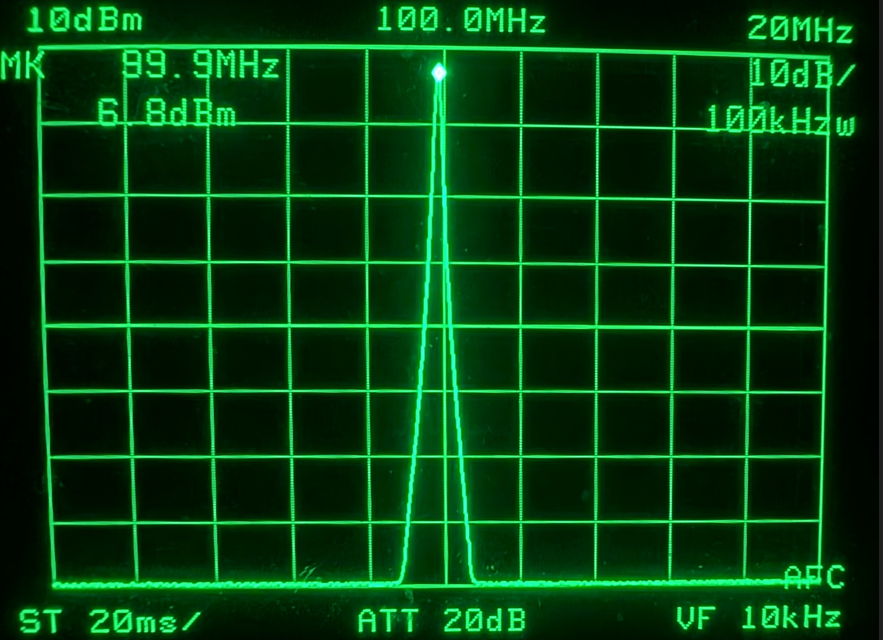

100MHz近傍の位相ノイズが気になる。

100MHzの基本信号レベルは12dBm程度となる。

si5153aはクロックジェネレータであり、低ジッタになるよう分周品を選択したのだが、やはりキャリア信号近傍の位相ノイズ雑音が発生していた。キャリア信号に対して70dB弱のレベルであるが、これがどれだけ全体の精度に影響するか引き続き注意していきたい。

またこのもう一つのSGとしてAD9959を使用したものがあり、これはDDS方式なので、基本位相ノイズはsi5153よりも小さいことが期待できる。一方で少し大きなことと、デバイスとして効果かつ複雑だというデメリットもある。